因为专业

所以领先

Flip-chip倒装封装作为半导体芯片封装的关键技术之一,其核心优势在于通过创新的互连方式突破了传统封装的性能瓶颈。以下是其关键选择依据及技术解析:

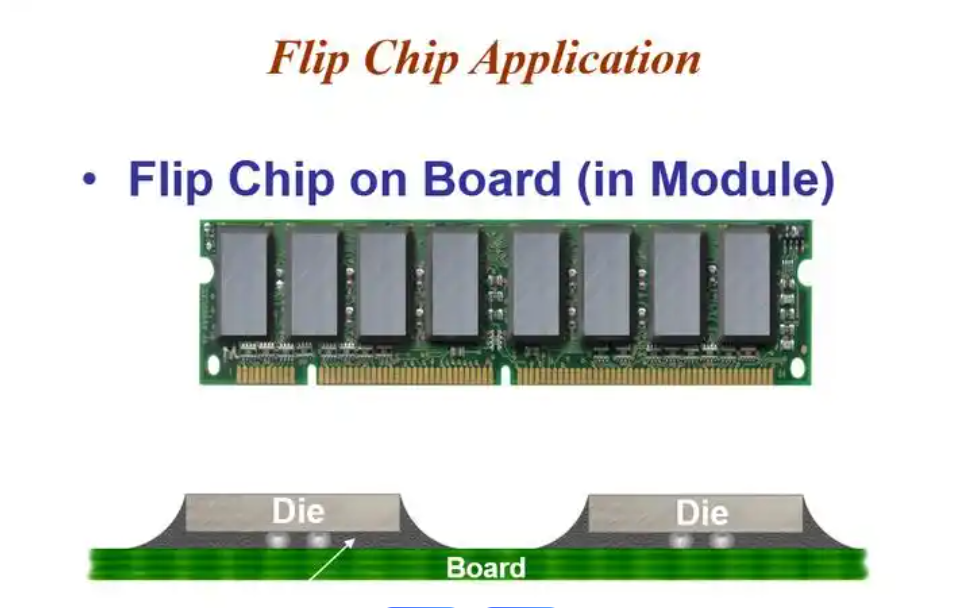

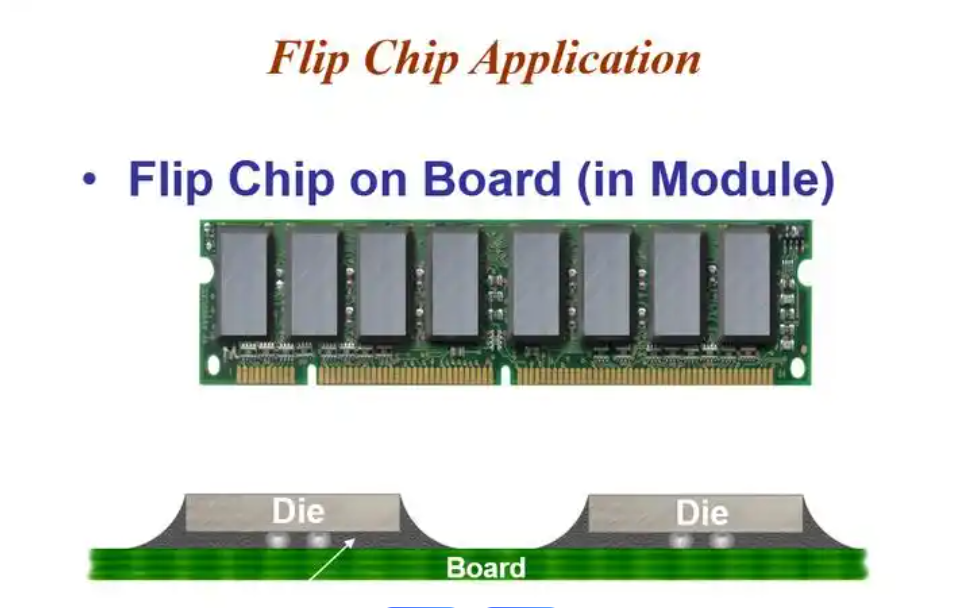

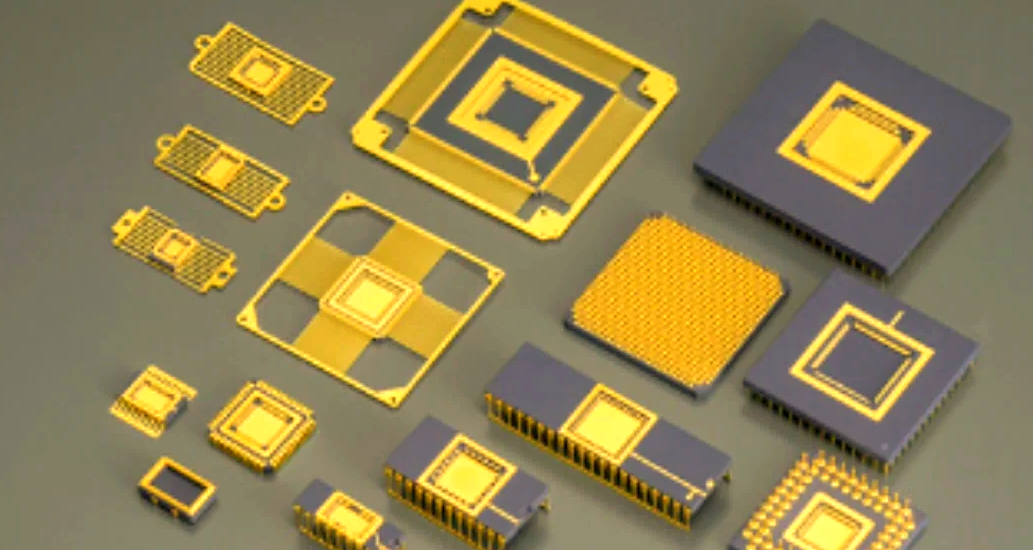

倒装封装结构

芯片通过凸点(Bump)直接倒装在基板上,省去传统引线键合步骤,实现芯片与基板的面对面连接。

凸点制作:在芯片I/O焊盘上沉积金属凸点(如锡、铅、金合金),需进行UBM(Under Bump Metallization)处理以增强附着力。

对准与贴装:通过高精度设备确保芯片与基板的对准,避免连接不良。

底部填充:填充芯片与基板间的空隙,增强机械强度并吸收热应力。

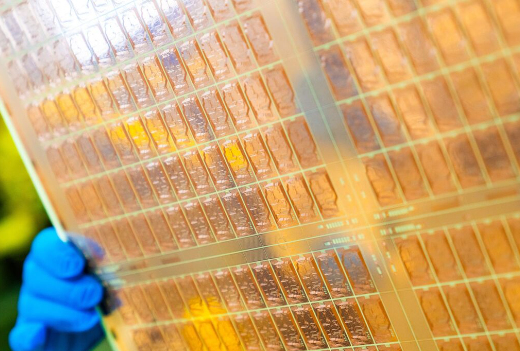

晶圆级封装(WLCSP)

在晶圆级完成凸点制作和测试,切割后直接倒装,显著降低成本并提升良率。

高密度互连与电性能提升

凸点阵列缩短信号路径,减少寄生电容/电感,支持高频高速信号传输。

适用于I/O数超过1000的高密度芯片,如GPU、FPGA。

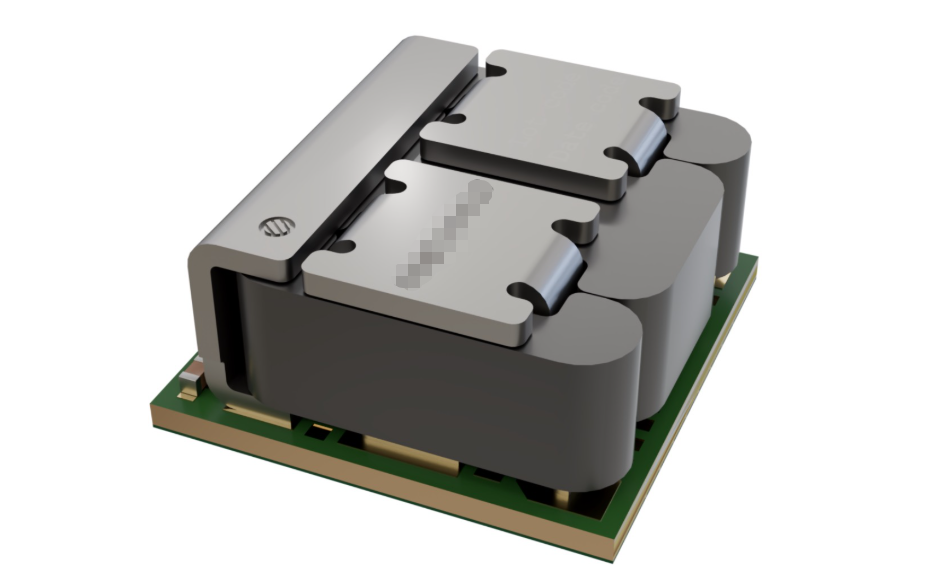

散热性能优化

芯片直接接触基板,热阻降低50%以上,散热效率优于引线键合封装,适用于高功率芯片(如25W以上)。

小型化与轻量化

封装体积接近芯片尺寸,厚度减少30%-50%,满足移动设备和可穿戴设备需求。

可靠性增强

芯片与基板紧密结合,抗冲击性提升,适用于工业和汽车电子。

高性能计算

CPU、GPU等处理器依赖倒装封装实现高带宽和低延迟。

存储器芯片

DRAM、NAND Flash通过倒装封装提升散热和信号完整性,三星、SK海力士等厂商广泛采用。

5G通信与AI芯片

支持高频信号传输和高密度集成,适用于基带芯片、AI加速器。

传感器与图像芯片

焦平面探测器等通过倒装焊实现系统级封装(SIP)。

工艺复杂性

凸点制作精度:需优化电镀/光刻工艺,控制凸点尺寸和分布。

对准精度:采用激光对位和主动校正技术,误差控制在微米级。

散热与材料限制

热界面材料:使用高导热胶或嵌入式热电制冷器(如Nextreme的铜柱技术)。

基板材料:陶瓷基板(高导热)与有机基板(低成本)的平衡选择。

成本与可维修性

规模化生产:通过晶圆级封装(WLCSP)降低单位成本。

模块化设计:采用扇出型封装(Fan-Out WLCSP)提升维修可能性。

微型化与高密度化

突破凸点间距极限(<40μm),支持Chiplet异构集成。

材料创新

研发无铅凸点、铜柱凸点及低温共晶焊料,降低环境污染和成本。

散热技术突破

集成微流道散热或热管技术,应对3D堆叠芯片的热管理需求。

智能化工艺

AI驱动的工艺参数优化和缺陷检测,提升良率至99%以上。

Flip-chip倒装封装通过结构创新和工艺优化,成为高端芯片封装的首选方案。其在性能、散热和小型化方面的优势,结合未来技术演进,将持续推动半导体行业的微型化与高性能化发展。如需进一步了解具体工艺参数或应用案例,可参考138等来源。

Flip-chip倒装芯片清洗剂选择:

水基清洗的工艺和设备配置选择对清洗精密器件尤其重要,一旦选定,就会作为一个长期的使用和运行方式。水基清洗剂必须满足清洗、漂洗、干燥的全工艺流程。

污染物有多种,可归纳为离子型和非离子型两大类。离子型污染物接触到环境中的湿气,通电后发生电化学迁移,形成树枝状结构体,造成低电阻通路,破坏了电路板功能。非离子型污染物可穿透PC B 的绝缘层,在PCB板表层下生长枝晶。除了离子型和非离子型污染物,还有粒状污染物,例如焊料球、焊料槽内的浮点、灰尘、尘埃等,这些污染物会导致焊点质量降低、焊接时焊点拉尖、产生气孔、短路等等多种不良现象。

这么多污染物,到底哪些才是最备受关注的呢?助焊剂或锡膏普遍应用于回流焊和波峰焊工艺中,它们主要由溶剂、润湿剂、树脂、缓蚀剂和活化剂等多种成分,焊后必然存在热改性生成物,这些物质在所有污染物中的占据主导,从产品失效情况来而言,焊后残余物是影响产品质量最主要的影响因素,离子型残留物易引起电迁移使绝缘电阻下降,松香树脂残留物易吸附灰尘或杂质引发接触电阻增大,严重者导致开路失效,因此焊后必须进行严格的清洗,才能保障电路板的质量。

合明科技研发的水基清洗剂配合合适的清洗工艺能为芯片封装前提供洁净的界面条件。

合明科技运用自身原创的产品技术,满足芯片封装工艺制程清洗的高难度技术要求,打破国外厂商在行业中的垄断地位,为芯片封装材料全面国产自主提供强有力的支持。

推荐使用合明科技水基清洗剂产品。

![[x]](/template/default/picture/closeimgfz1.svg)